## 27.1 A 250kHz-BW 93dB-SNDR 4<sup>th</sup>-Order Noise-Shaping SAR Using Capacitor Stacking and Dynamic Buffering

Jiaxin Liu<sup>1</sup>, Dengquan Li<sup>2</sup>, Yi Zhong<sup>1</sup>, Xiyuan Tang<sup>3</sup>, Nan Sun<sup>1,3</sup>

<sup>1</sup>Tsinghua University, Beijing, China <sup>2</sup>Xidian University, Xi'an, China <sup>3</sup>University of Texas, Austin, TX

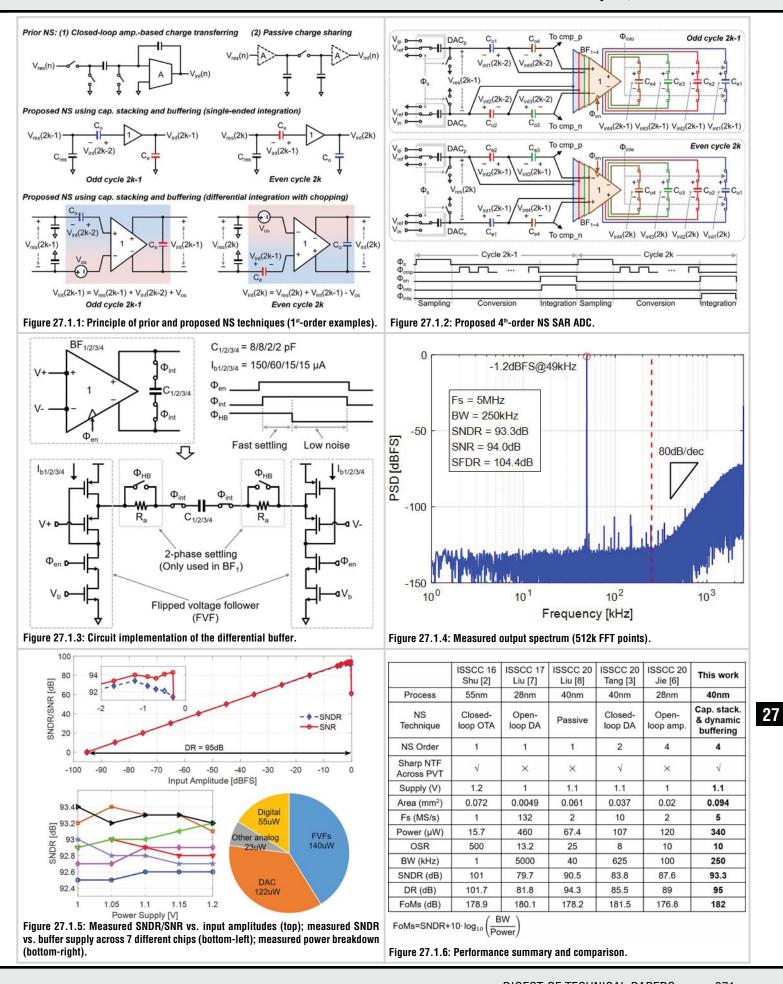

The noise-shaping (NS) SAR is an emerging hybrid architecture that aims to combine the benefits of both SAR and  $\Delta\Sigma$  ADCs [1-8]. The key in an NS SAR is the NS filter. As shown in Fig. 27.1.1, prior NS filter techniques can be classified into two types. The first way is to use a closed-loop amplifier-based integrator [1-3]. With sufficient gain of the amplifier, this type of integrator can realize a sharp noise transfer function (NTF). However, the high-gain multi-stage amplifier produces large noise, is power-consuming and unfriendly to technology scaling [2,3]. The second way is to use passive charge sharing to perform error feedback [4-6] or integration [7,8]. The fully passive filter avoids using closed-loop amplifiers, but it has signal attenuation issue and the resulting NTF is mild [4]. Also, due to the lack of effective gain, it suffers from large comparator noise. To improve the NTF and noise suppression capability, some works place an open-loop amplifier before the passive filter [5-7], or implement a passive gain after it [8]. However, the gain of an open-loop amplifier is sensitive to PVT variations, and the passive gain method suffers from severe parasitic effects when a large gain is required.

This paper presents an efficient way to implement a high-order and robust NS filter. It realizes an integrator by stacking the residue capacitor with the integration capacitor, and storing the stacking result through a unity-gain buffer. A source follower can be used as the buffer, which is simple and PVT robust. This NS filter does not rely on any amplifier, and realizes a sharp NTF with zeros close to the unit circle. It has low hardware complexity, and is easy to extend to high order. A 4<sup>th</sup>-order NS SAR is implemented in this work. It achieves 93.3dB SNDR over 250kHz bandwidth at the OSR of 10 while consuming 340µW power, leading to a Schreier FoM of 182dB.

0549-C To illustrate the operation principle, the 1<sup>st</sup>-order examples of the proposed NS technique  $\overline{\infty}$  operation cycle 2k-1, the integration capacitor C<sub>0</sub> is stacked with the residue capacitor  $C_{0}$  is stacked with the residue capacitor  $C_{0}$  is stacked with the residue capacitor  $C_{res}$ , obtaining the sum of the residue voltage  $V_{res}(2k-1)$  and the previous integration voltage V<sub>int</sub>(2k-2). The sum is the ideal integration result, but it cannot be directly used  $\frac{1}{2}$  voltage  $v_{int}(2k-2)$ . The sum is the ideal integration result, but it cannot be directly used  $\frac{1}{2}$  in consequent ADC conversions. To address this issue, another integration capacitor  $C_e$ is used to store the integration result  $V_{int}(2k-1) = V_{res}(2k-1) + V_{int}(2k-2)$  through a unitygain buffer. A ping-pong operation is performed between  $C_o$  and  $C_e$ . In the next even Signin buffer. A ping-pong operation is performed between  $G_0$  and  $G_0$ . In the next even  $\mathcal{G}_0$  by the next even  $\mathcal{G}_0$  is used to store the new integration result  $V_{int}(2k) = V_{res}(2k) + V_{int}(2k-1)$ . In this way, the ideal integration is realized without using  $\mathcal{L}_{int}(\mathcal{L}_{int}) = v_{res}(\mathcal{L}_{int}) + v_{int}(\mathcal{L}_{int})$ . In this way, the decar integration is realized without using  $\mathcal{L}_{int}$  a closed-loop amplifier. A problem with the single-ended integration is that it is prone  ${\mathbb F}$  to saturation due to the DC component across the integration capacitor, which includes Ethe buffer offset and the common-mode voltage mismatch at both ends of the capacitor. This problem can be solved by performing differential integration (placing the integration Entry problem can be solved by performing understanding and chopping the buffer and integration capacitors. Chopping also addresses the flicker noise of the buffer. In addition, for the same kT/C noise budget, the total integration capacitor size in a  ${\mathbb Z}$  differential ADC can be 4× reduced by using differential integration, comparing with that using single-ended integration.

The proposed 4<sup>th</sup>-order NS SAR ADC is shown in Fig. 27.1.2 (the comparator and SAR logic are not shown for simplicity). Four groups of capacitors and differential buffers  $(C_{01}-BF_1-C_{el}, i=1-4)$  form a 4<sup>th</sup>-order integration network. During an odd operation cycle  $(C_{01}-BF_1-C_{el}, i=1-4)$  form a 4<sup>th</sup>-order integration network. During an odd operation cycle  $(C_{01}-BF_1-C_{el}, i=1-4)$  form a 4<sup>th</sup>-order integration network. During an odd operation cycle  $(DAC_{p}, 16pF)$ , while  $C_{02}$  and  $C_{03}$  are stacked over DAC<sub>n</sub>. Since  $C_{01-4}$  hold the previous integration results  $V_{int1-4}(2k-2)$ , the stacking operation realizes the addition of the present input signal with  $V_{int1-4}(2k-2)$ . Therefore, a standard 1-input-pair comparator connected between the right sides of  $C_{04}$  and  $C_{03}$  can be used for the SAR conversion. At the end of SAR conversion, the residue voltage  $V_{res}(2k-1)$  is obtained across the top plates of the DACs, and the buffers are enabled. BF<sub>1</sub> (connected across  $C_{01}$ -DAC<sub>p</sub>-DAC<sub>n</sub>) delivers the 1<sup>st</sup>-order integration result  $V_{int1}(2k-1) = V_{res}(2k-1) + V_{int1}(2k-2)$  to  $C_{e1}$ , BF<sub>2</sub> (connected across  $C_{01}$ -DAC<sub>p</sub>-DAC<sub>n</sub>- $C_{02}$ ) delivers the 2<sup>st</sup>-order integration result  $V_{int2}(2k-1) = V_{res}(2k-1)$  $V_{int1}(2k-2) + V_{int2}(2k-2)$  to  $C_{e2}$ , BF<sub>3</sub> (connected across  $C_{01}$ -DAC<sub>p</sub>-DAC<sub>n</sub>- $C_{02}$ - $C_{03}$ ) delivers the 3<sup>st</sup>-order integration result  $V_{int3}(2k-1) = V_{res}(2k-1) + V_{int1}(2k-2) + V_{int2}(2k-2)$  $V_{int3}(2k-2)$  to  $C_{e3}$ , and BF<sub>4</sub> (connected across  $C_{04}$ - $C_{01}$ -DAC<sub>p</sub>-DAC<sub>n</sub>- $C_{02}$ - $C_{03}$ ) delivers the 4<sup>m</sup>-order integration result V<sub>int4</sub>(2k-1) = V<sub>res</sub>(2k-1) + V<sub>int1</sub>(2k-2) + V<sub>int2</sub>(2k-2) + V<sub>int2</sub>(2k-2) + V<sub>int4</sub>(2k-2) to C<sub>e4</sub>. After integrations, the buffers are disabled to save power. During the next even cycle 2k, C<sub>e1-4</sub> are stacked over the DACs, and C<sub>o1-4</sub> are used to store the new integration results V<sub>int1-4</sub>(2k). Also, the integration network (C<sub>e1-4</sub>-BF<sub>1-4</sub>-C<sub>o1-4</sub>) is flipped to perform chopping.

The differential buffer consists of a pair of flipped voltage followers (FVFs), as shown in Fig. 27.1.3. The FVFs are dynamically controlled by  $\Phi_{en}$ . They are only powered during the integration phase (25% of an entire ADC operation cycle). Compared with a conventional source follower, the FVF provides smaller output resistance and therefore faster settling, but this is at the cost of larger noise. To reduce noise, the 2-phase settling technique is used [6]. A switch-controlled resistor  $R_a$  is added at the FVF output to adjust its bandwidth. During the first 15ns of the integration phase,  $R_a$  is bypassed to enable fast settling. During the remaining 35ns of the integration phase,  $R_a$  is switched in to limit the noise bandwidth. In this way, the proposed buffer combines the benefits of fast settling and low noise. The 2-phase settling is only used in BF<sub>1</sub>, because the noise introduced by BF<sub>2-4</sub> can be shaped and thus is negligible. The integration capacitors and bias currents for BF<sub>1/2/3/4</sub> are C<sub>1/2/3/4</sub>=8/8/2/2pF, I<sub>b1/2/3/4</sub>=150/60/15/15µA, respectively. Monte Carlo simulation shows that the gain of the FVF is around 0.95 with 1% 3σ variation, which ensures a sharp and robust NTF.

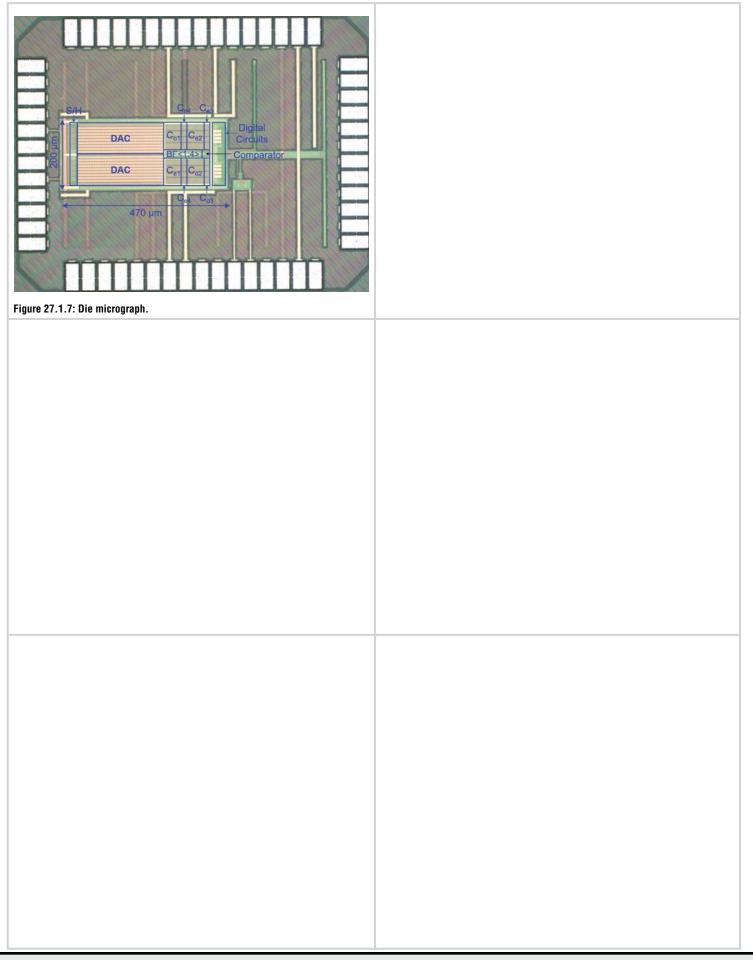

Fabricated in 40nm CMOS, the prototype occupies  $0.094mm^2$  (Fig. 27.1.7) and consumes  $340\mu$ W of power when operating under a 1.1V supply and a 5MS/s sampling rate. The DAC mismatch is addressed by a foreground calibration. Figure 27.1.4 shows the measured output spectrum with a 49kHz -1.2dBFS input. The SNDR, SNR and SFDR over a 250kHz bandwidth are 93.3dB, 94dB and 104.4dB, respectively. Figure 27.1.5 shows the measured SNDR/SNR versus input amplitude. The dynamic range (DR) is 95dB. To prove the robustness of the proposed NS technique, the measured SNDRs of 7 chips versus FVF supply are also given in Fig. 27.1.5. It shows that the SNDR variation is within 1dB across the 7 chips, and is within 0.3dB against ±10% supply changes.

Figure 27.1.6 compares this work with prior publications. By using capacitor stacking and buffering for integration, the proposed NS SAR avoids the signal attenuation of passive charge sharing. Also, it does not require a closed-loop or open-loop amplifier; the former is complex and power-consuming while the latter suffers from gain variation and leads to NTF variation. The simple source followers are used as the buffers in this work. Due to the stable unity gain of source followers, the proposed NS SAR realizes a robust and sharp NTF. The architecture is compact and easy to extend to high order. This work is the first NS SAR ADC that achieves >90dB SNDR with >100kHz bandwidth.

## Acknowledgement:

This work was supported by NSFC under Grants 61904094 and 61934009, Beijing National Research Center for Information Science and Technology, and Beijing Innovation Center for Future Chip.

## References:

[1] J. Fredenburg and M. Flynn, "A 90MS/s 11MHz Bandwidth 62dB SNDR Noise-Shaping SAR ADC," *ISSCC*, pp. 468–470, Feb. 2012.

[2] Y. Shu et al., "An Oversampling SAR ADC with DAC Mismatch Error Shaping Achieving 105dB SFDR and 101dB SNDR over 1kHz BW in 55nm CMOS," *ISSCC*, pp. 458–459, Jan. 2016.

[3] X. Tang et al., "A 13.5b-ENOB Second-Order Noise-Shaping SAR with PVT-Robust Closed-Loop Dynamic Amplifier," *ISSCC*, pp. 162–164, Feb. 2020.

[4] Z. Chen et al., "A 9.35-ENOB, 14.8 fJ/conv.-step fully-passive noise-shaping SAR ADC," *IEEE Symp. VLSI Circuits*, pp. C64–C65, June 2015.

[5] S. Li et al., "A 13-ENOB 2nd-Order Noise-Shaping SAR ADC Realizing Optimized NTF Zeros Using an Error-Feedback Structure," *ISSCC*, pp. 234–236, Feb. 2018.

[6] L. Jie et al., "A 4th-Order Cascaded-Noise-Shaping SAR ADC with 88dB SNDR Over 100kHz Bandwidth," *ISSCC*, pp. 160-162, Feb. 2020.

[7] C. C. Liu and M. C. Huang, "A 0.46mW 5MHz-BW 79.7dB-SNDR Noise-Shaping SAR ADC with Dynamic-Amplifier-Based FIR-IIR filter," *ISSCC*, pp. 466-467, Feb. 2017.

[8] J. Liu et al., "A 40kHz-BW 90dB-SNDR Noise-Shaping SAR with 4× Passive Gain and 2nd-Order Mismatch Error Shaping," *ISSCC*, pp. 158-160, Feb. 2020.

ISSCC 2021 / February 18, 2021 / 7:00 AM